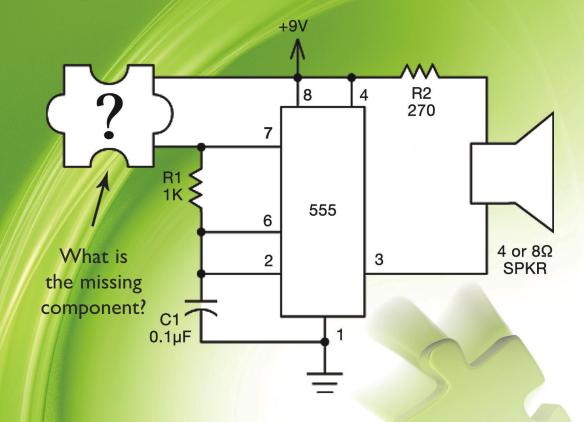

What a cap-astrophe! Pg 60

EDN.comment Pg 6

The best solution brings accuracy Pg 18

Inside Nanotechnology Pg 20

Issue 10/2010

www.edn.com

Mechatronics in Design Pg 26

Design Ideas Pg 49

### SENSORS EMPOWER THE "INTERNET OF THINGS" Page 32

RECONFIGURABLE

SINGLE-CHIP RADIOS Page 29

Power management for optimal power design

Page 40

# CONTRACTOR CONTRACTOR

Than

More

BULGIN

red lipn

Pomona

roducts in Stoc

Dialiahi

icrosemi

Ctorm

### 45,000 NEW Products Added in the Last 90 DAYS

VFN

JRC

H Littelfuse

SEA

8

# #1 Breadth of Product Line#1 Availability of Product#1 Overall Performance

Source: EETImes Distribution Study, August 2009

The industry's broadest product selection available for immediate delivery

### www.digikey.com 1.800.344.4539

\*Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2010 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

INCH

ΔΝΥΟ

Richc

Re

APEM

ENFIS

Ioneywell

# When it matters most.

### **Reliability.**

Cirrus Logic's Apex Precision Power<sup>®</sup> voltage references have no peer with high-accuracy, ultra low-drift that's best-in-class.

#### THE VRE100 SERIES PRECISION VOLTAGE REFERENCES

The Cirrus Logic family of Apex Precision Power products makes designing with power simple! The VRE100 series of high-precision voltage references offers best-in-class performance for low temperature drift by minimizing the impact of operating conditions on voltage delivery over time.

- · Ultra stable +10 V (VRE100), -10 V (VRE101) and ±10 V (VRE102) outputs

- · Initial accuracy a low ±1.0 mV

- · Temperature coefficients as low as 1.0 ppm/°C

- · Extremely low drift over the full military temperature range

The superior quality and reliability of these off-the-shelf solutions can eliminate design cycle headaches and speed your time to market.

### LEARN MORE AT: WWW.cirrus.com/ednvre

© 2010 Cirrus Logic, Inc. All rights reserved. Cirrus Logic, Cirrus, the Cirrus Logic logo designs, Apex Precision Power, Apex and the Apex Precision Power logo designs are trademarks of Cirrus Logic, Inc. All other brands and product names may be trademarks or service marks of their respective owners. EDN05272010

### Sensors empower the "Internet of Things"

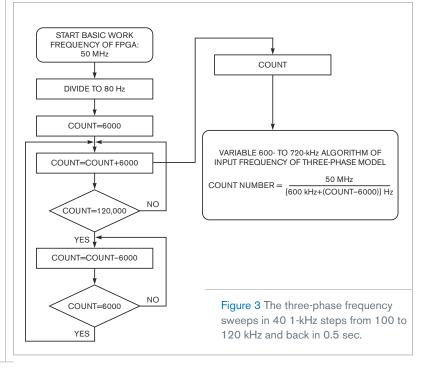

B 2 Where are you? Who are you? What are you doing? Assume that someone or something—an individual, a company, or a government—knows the answer to all of these questions. Is this scenario a nightmare or the next obvious step to defining individuals in our society? Welcome to the "Internet of Things."

> By Margery Conner, Technical Editor

### Reconfigurable single-chip radios

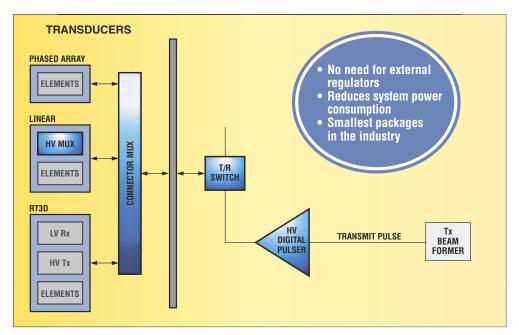

29 Extreme integration packs an extensive number of communications functions into a high-performance, low-area, lowpower IC.

> By Jan Craninckx and Piet Wambacq, IMEC

- National Semiconductor, Silicon Labs team up for power-brick reference design

- 12 Energy-measurement chip meters power-distribution units for server farms

- 12 Olympus and Calibre speed closure

- 14 Apple buys second chip company

- 14 Redpine, Renesas team on embedded Wi-Fi

- 15 3-D system uses optical fiber to provide new options for photovoltaics

- 16 Voices: The MathWorks' Silvina Grad-Freilich talks high-performance computing

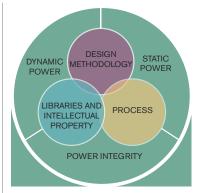

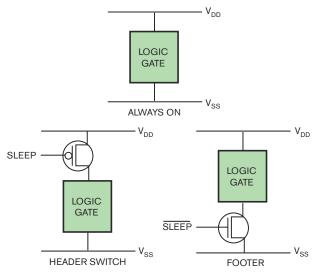

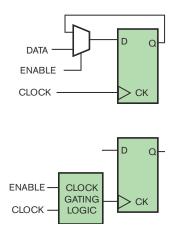

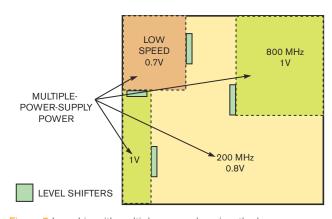

### Power management for optimal power design

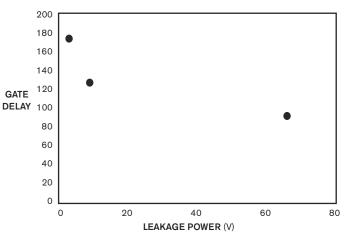

40<sup>A</sup> holistic approach to power management, from transistors to full-chip techniques, is necessary for meeting today's power-management goals.

> By Prasad Subramaniam, eSilicon Corp

### DESIGNIDEAS

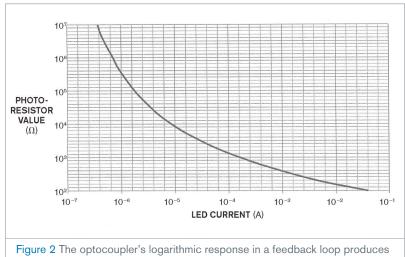

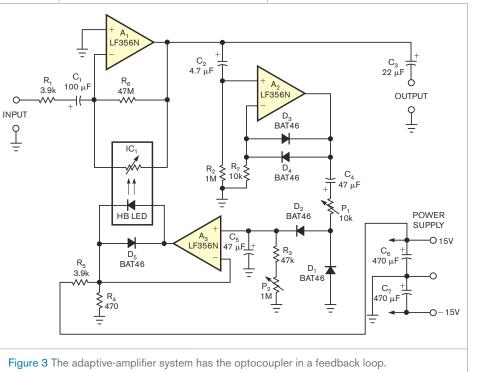

49 Photoresistor provides negative feedback to an op amp, producing a linear response

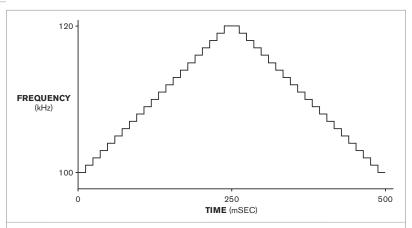

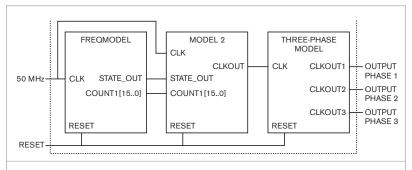

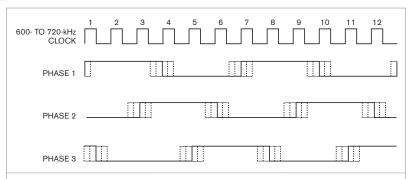

54 Three-phase digital-signal generator sweeps frequency

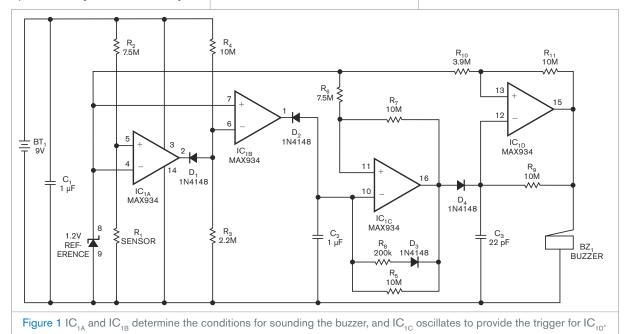

56 Water-leak detector uses 9V batteries

Send your Design Ideas to edndesignideas@cancom.com.

### The Newest Products For Your Newest Designs

We're sensitive to your new technology needs.

💤 freescale

RD3965MMA7660FC: ZSTAR3 with MMA7660FC Accelerometer mouser.com/freescalerd3965mma7660fc

Honeywell Sensing and Control

Advanced Magnetic Sensors mouser.com/Honeywellmagneticsensors

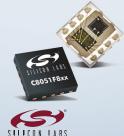

QuickSense<sup>™</sup> Human Interface Solutions mouser.com/silabsquicksense

🐠 Міскоснір

PICDEM<sup>™</sup> Inductive Touch Development Kit mouser.com/microchip/a

WARNING: Designing with Hot, New Products May Cause a Time-to-Market Advantage.

With the newest sensing products and technologies, Mouser is committed to Engineers. Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 400 leading suppliers.

a tti company

.

mouser.com (800) 346-6873

Jouser and Mouser Electronics are registered trademarks of Mouser Electronics, Inc. Other products, logos, and company names mentioned herein, may be trademarks of their respective owners.

### contents 5.27.10

### **DEPARTMENTS & COLUMNS**

6 EDN.comment: MEMS, asynchronous logic enter SOC-design flow

- 18 Baker's Best: The best solution brings accuracy

- 20 Inside Nanotechnology: Nanopatterning: getting the right objects small

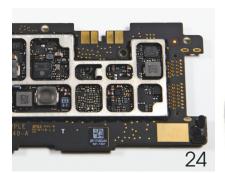

- 24 Prying Eyes: Apple's iPad: new computing form factor or passing fad?

- 26 Mechatronics in Design: Handling the World Wide Web

- 58 Product Roundup: Sensors/Transducers, Power Sources

- 60 Tales from the Cube: What a cap-astrophe!

### **EDN**) online contents

### www.edn.com

### READ ANY GOOD DESIGN IDEAS LATELY?

10V

*EDN*'s Design Ideas, contributed by practicing electronics engineers, deliver practical, innovative circuit designs in a concise format complete with circuit schematic diagrams, application details, and even software code. ->www.edn.com/designideas

### Designing with EDS

Lighting for the 21st century

Practical, inexpensive HB LEDs (highbrightness light-emitting diodes) are here. Now, what can we do with them, and what will be their impact on electronics and consumers? Read more online. →www.edn.com/leds

### **Readers' Choice**

Here is a selection of recent articles receiving high traffic on www.edn.com:

Nokia claims Apple iPad, iPhone infringe its patents

→www.edn.com/article/CA6728169

Wi-Fi, WiGig alliances team for wireless at 60-GHz band →www.edn.com/article/CA6728319

EDN names winners of 20th annual Innovation Awards

→www.edn.com/article/CA6727246

Obama and the environment: New policies could produce more electronics regulation, opportunity →www.edn.com/article/CA6631539

EDN® (ISSN#Q012-7515) is published semimonthy, 24 times per year, by Canon Communications LLC, 11444 W. Olympic BVd, Los Angeles, CA 90064-1549, 310/445-4200; FAX 310/445-4299, Periodicals postage paid at Los Angeles, California, and at additional mailing offices. SUBSCRIPTIONS-Free to qualified subscribers as defined on the subscription card. Rates for nonqualified subscriptions, including all issues: US, \$179.99 one year; Canada, \$229.99 one year (includes 7% GST, GST# 123397457); Mexico, \$229.99 one year; air expedited, \$399.99 one year; Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 763/746-2792. Email: EDN@kmpsgroupc.cm. CHANGE OF ADDRESS-Notices should be sent promptly to PO Box 47461, Pymouth, MN 55447. Please provide old mailing labels as well as new address. Allow two months for change. NOTICE-Every precaution is taken to ensure accuracy of content; however, the publishers cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER-Send address changes to EDN, PO Box 47461, Pymouth, MN 55447. Canada Post: Publications Mail Agreement 40685520. Return undeliverable Canadian addresses to RCS International, Box 697 STN A, Windsor, Ontario N9A 6N4. Copyright 2010 by Canon Communications LLC. All rights reserved. Reproduction in whole or part without written permission is prohibited. Volume 56, Number 10 (printed in USA).

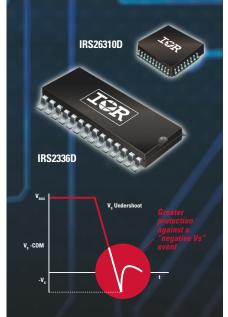

### Rugged, Reliable Motor Control by Design

Protect Against Catastrophic Events with IR's High Voltage ICs

#### Features

- Designed and characterized to be tolerant to repetitive negative Vs transient voltage

- Characterized to withstand short circuit events

- Tolerant to large dV/dt

- Integrated bootstrap functionality

- Advanced input filter

- Fully operational up to 600 V

For more information call 1.800.981.8699 or visit http://www.irf.com

International **ICR** Rectifier THE POWER MANAGEMENT LEADER

### BY RON WILSON, EXECUTIVE EDITOR

### MEMS, asynchronous logic enter SOC-design flow

wo companies that exhibited at the Embedded Systems Conference in San Jose, CA, in April have similar objectives but for different technologies. Coventor, a vendor of CAD and analysis tools for creating MEMS (microelectromechanical-system) devices, described a plan for bringing MEMS design into the standard CMOS SOC (system-onchip) flow. Asynchronous-logic-design shop Tiempo showed a flow that facilitates development of large asynchronous blocks within a conventionally synchronous SOC.

Coventor provides MEMS-creation tools popular with specialists. C-Ware, for example, is a multiphysics simulator for modeling MEMS structures, and SEMulator is a 3-D-process-simulation tool for designing process steps to create the structures. Together with a 3-D-design-entry tool, the suite allows MEMS experts to create structures, investigate their behavior, and craft a manufacturing flow for them.

The next logical step, according to Michael Jamiolkowski, Coventor's president and chief executive officer, is to create behavioral models of the structures in C++ and electrical models in an accepted SOC-design environment and drop the designs into a library as reusable, parameterized IP (intellectual property). That task is the function of Coventor's new tool, MEMS+, a complete subflow for creating MEMS elements and integrating them into Cadence's Virtuoso.

MEMS+ includes a schematic generator and modeler, managers to handle materials and process data, a 3-D viewer, and layout and DRC (designrule-checking) tools. Using this package, MEMS experts can create a new device design, along with a schematic The emphasis in integration is slowly shifting toward integration of new kinds of devices that haven't previously been on the die at all.

symbol, an electrical netlist, a parameterized cell, DRC and LVS (layoutversus-schematic) data, and behavioral and electrical models for Spectre and UltraSim.

In some ways, Tiempo's task is similar. The company's technology uses a data-encoding scheme to indicate to a receiving block when valid data arrives from the transmitting block. The approach requires an area overhead of 20 to 50% but significantly reduces both static and dynamic power; is virtually insensitive to pressure, voltage, and temperature variations; offers sharply reduced emissions; and can detect some security attacks.

Tiempo has for some time used the

technology to produce IP, including a 16-bit microcontroller and a cryptoprocessor for contactless smart cards. Now, the company is offering a flow to make asynchronous design accessible to designers who don't know—and don't care to learn-the fine points of the technology. The flow begins with a transaction-level description of the desired block in SystemVerilog. Tiempo's tools synthesize the SystemVerilog code into a Verilog netlist, using a library of combinatorial and asynchronous cells. Verification is through either mixed-mode Verilog/SystemVerilog simulation or FPGA prototype.

The flow puts complex asynchronous blocks within the reach of ordinarily skilled SOC-design teams, according to Serge Maginot, Tiempo's president and chief executive officer. Designers need to learn only how to write a transaction-level model in which concurrent processes communicate through channels using read and write primitives, how to write interfaces between the asynchronous block and its synchronous surroundings, how to create timing constraints for the interface-resynchronization points, and how to create throughput constraints for the asynchronous paths.

In a way, both tool-flow announcements are signs of the times. The emphasis in integration is slowly shifting away from more gates, more memory, and more CPU cores and toward integration of new kinds of devices that haven't previously been on the die at all. The range and quality of passive components available to custom designers have been gradually increasing. Now, we are starting to see thirdparty tools for MEMS and for the asynchronous blocks that have long been the purview of only the largest and best-funded design teams in organizations such as Intel and IBM. More than Moore's Law is upon us.EDN

Contact me at ronald.wilson@cancom.

Yes, chip inductors are among Coilcraft's biggest sellers. But did you know we also offer a full range of other RF products like these?

They're all in stock for immediate shipment and all available as free samples for testing and evaluation.

For the full picture, visit www.coilcraft.com/RF

#### **Broadband Conical Inductors**

High impedance from 10 MHz to 40 GHz. Perfect for RF to millimeter-wave choking and bias tees. Available with leads or in surface mount versions for ruggedness and easy mounting.

#### **RFID Transponder Coils**

A variety of antenna coils for 125 kHz systems. Automotive grade models for tire pressure and keyless entry applications.

#### Air Core Inductors

For the highest possible Q and current handling, nothing beats our air core "Spring" inductors. New models offer more inductance values and smaller size.

#### Wideband Transformers

Our low insertion loss transformers come in a wide range of turns ratios. Use for baluns, isolation or impedance matching.

## Some people only think of us for chip inductors.

PUBLISHER, EDN WORLDWIDE Russell E Pratt, 1-781-869-7982;

russell.pratt@cancom.com

ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes, 1-925-736-7617; judy.hayes@cancom.com

EDITOR-IN-CHIEF, EDN WORLDWIDE Rick Nelson, 1-781-869-7970;

richard.nelson@cancom.com EXECUTIVE EDITOR

Ron Wilson, 1-510-744-1263; ronald.wilson@cancom.com

MANAGING EDITOR

Amy Norcross 1-781-869-7971; fax: 1-781-862-4853; amy.norcross@cancom.com Contact for contributed technical articles

#### SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@cancom.com MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS Brian Dipert, Senior Technical Editor 1-916-760-0159; brian.dipert@cancom.com

NEWS Suzanne Deffree, Managing Editor 1-631-266-3433; suzanne.deffree@cancom.com

POWER SOURCES, ONLINE INITIATIVES Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; margery.conner@cancom.com

DESIGN IDEAS EDITOR Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@cancom.com

SENIOR ASSOCIATE EDITOR Frances T Granville 1-781-869-7969; fax: 1-781-862-4853; frances.granville@cancom.com

CONSULTING EDITOR Jim Williams, Staff Scientist, Linear Technology edn.editor@cancom.com CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Robert Cravotta, robert.cravotta@embeddedinsights.com

**COLUMNISTS** Howard Johnson, PhD, Signal Consulting

Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap Kevin C Craig, PhD, Marquette University

PRODUCTION Dorothy Buchholz, Group Production Director 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

EDN EUROPE Graham Prophet, Editor, Reed Publishing gprophet@reedbusiness.com

> EDN ASIA Luke Rattigan, Chief Executive Officer Iuke.rattigan@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@rbichina.com.cn Jeff Lu, Executive Editor jefflu@rbichina.com.cn

EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

EXECUTIVE OFFICERS

Charles G. McCurdy, Chief Executive Officer Daniel Koskovich, Chief Financial Officer Ron Wall, Senior Vice President, Publications Kevin O'Keefe, Senior Vice President, Events Division Roger Burg, Vice President, Operations Jason Brown, Vice President, E-Media

EDN. 33 Hayden Avenue, Lexington, MA 02421. www.edn.com. Subscription inquiries: 1-763-746-2792; EDN@kmpsgroup.com. Address changes: Send notice promptly to PO Box 47461, Plymouth, MN 55447. Please provide an old mailing label as well as your new address. Allow two months for the change. Canon Communications LLC, 11444 W. Olympic Boulevard, Los Angeles, CA 90064-1549; 1-310-445-4200; fax: 1-310-445-4299.

Download the AP Applied on high speed, low cost production test a www.ap.com/APApplied\_Production

### Make an impact

### Unleash the power of CST STUDIO SUITE®,

### the No 1 technology for electromagnetic simulation.

$\rightarrow$  Get equipped with leading edge EM technology. CST's tools enable you to characterize, design and optimize electromagnetic devices all before going into the lab or measurement chamber. This can help save substantial costs especially for new or cutting edge products, and also reduce design risk and improve overall performance and profitability.

Involved in signal or power integrity analysis? You can read about how CST technology was used to simulate and optimize a digital multilayer PCB's performance at www.cst.com/pcb. If you're more interested in EMC/EMI or microwave components, we've a wide range of worked application examples live on our website at www.cst.com/apps.

Now even more choice for SI/PI simulation. The extensive range of tools integrated in CST STUDIO

SUITE enables numerous applications to be analyzed without leaving the familiar CST design environment. This complete technology approach enables unprecedented simulation reliability and additional security through cross verification.

$\rightarrow$  Grab the latest in simulation technology. Choose the accuracy and speed offered by CST STUDIO SUITE.

CHANGING THE STANDARDS

### MEET THE GUY that ELIMINATED HIS TEAM'S MANUFACTURING VARIABILITY ISSUES.

FIX YOUR MANUFACTURING VARIABILITY PROBLEMS AND YOUR REPUTATION WILL PRECEDE YOU. If you're designing chips for high functionality, high speed and lower power consumption at the most advanced process nodes, you've got variability issues. We have the solution that will increase your yield, performance and prestige by a wide margin. Get more information at mentor.com/solutions/manufacturing-variability.

# EDITED BY FRAN GRANVILLE **INNOVATIONS & INNOVATORS**

### National Semiconductor, Silicon Labs team up for power-brick reference design

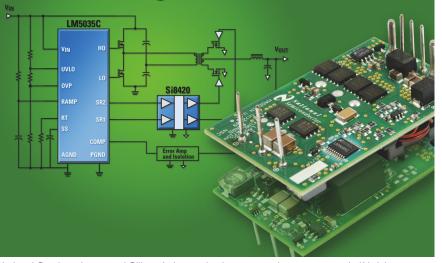

Silicon Laboratories and National Semiconductor have both contributed ICs to a power-brick reference design they co-developed. The brick uses a half-bridge architecture, with two FETs and two capacitors. The design targets use in networking, communications, and high-end server applications. It uses a National Semiconductor LM5035C PWM (pulse-width-modulation) controller and a Silicon Labs Si8420 isolator. The reference design produces 100W output power and comes in a 2.28×1.45×0.5-in. guarter-brick form factor. Input voltages to the brick can range from 36 to 75V, and it withstands 100V input transients. The board output is 3.3V at 30A, and efficiency is 89% at 30A and 92% at 15A output current.

Operating at a 400-kHz switching frequency, the device has a line regulation of 0.1% and

load regulation of 0.2%. The six-layer design uses 2- and 3-oz copper on the outer and inner layers, respectively. It requires 200 cfm of airflow to maintain thermal integrity and offers both undervoltage lockout and overvoltage protection on the input bus. The PWM chip integrates 2A half-bridge gate drivers. The board's designers used the Silicon Labs isolator to send secondary-synchronous-rectification gate-drive signals across the isolation boundary. An LM8261 op amp drives an NEC (www. nec.com) PS2811 optocoupler to provide isolation for the feedback signal. The LM5035CEval board costs \$135. The free reference-design files are available at National's Web site.

#### -by Paul Rako

### National Semiconductor. www.national.com.

Silicon Laboratories, www.silabs.com.

#### - FEEDBACK LOOP "Yes, we must continue to innovate, but it is important to not waste resources creating things that nobody

### wants."

-Engineer William Ketel, in EDN's Feedback Loop, at www. edn.com/article/CA6711874. Add your comments.

National Semiconductor and Silicon Laboratories have teamed up to create a half-brick-powersupply reference design and evaluation board.

### pulse

### Energy-measurement chip meters power distribution units for server farms

**M** mart power" usually brings to mind the smart power meters that will eventually sit at every business and home utility box and empower the smart grid. Another layer of applications for energy measurement exists, however: submetering, which measures power usage at the device or power-distribution level. A general utility meter measures power at the utility box when it comes into the facility-for example, a data farm. It next goes into

TERIDIAN SEMICONDUCTOR CORP 78/16618

a UPS (uninterruptible-power supply) and then on to the PDUs (power-distribution units), which act as smart power strips, sending the power to eight or as many as 64 channels, arriving ultimately at the power supplies in the servers themselves. At these huge megawatt installations, a variation of 1% in power efficiency is enough to win or lose business. However, without submetering at the PDU or power-supply level, the facility can't track power consumption to better than 5% accuracy.

To address these issues, the 78M6618 power-metering and -monitoring SOC (system on chip) from Teridian targets data-center PDUs as well as home and business smart power strips by enabling power metering, monitoring, and intelligent relay control of eight single-phase outlets simultaneously. You can control 32 or more channels by connecting multiple chips. The 6618 has an accuracy of greater than  $\pm 0.5\%$  over a 2000-to-1 dynamic range and includes self-calibration. It has a 22-bit delta-sigma ADC, 10 analog inputs, a precision voltage reference and digital

### C If you're looking for real-time, accurate measurement, get an AFE, which costs about \$1.

temperature compensation. It includes a 32-bit computation engine, a microprocessor core, and flash memory. It sells for \$5.90 (1000).

How does this pricing play in a world in which you can buy a Kill-a-Watt meter for \$25? Jay Cormier, vice president of the energy-measurement division at Teridian, which Maxim-IC recently acquired, puts pricing in perspective: "If you're looking for real-time, accurate measurement, the only way to do it today is to get an AFE [analog front end], which costs about \$1. For eight channels, you need eight AFEs, plus a microcontroller that adds another 50 cents. Plus, the AFEs require calibration. The 6618 comes with firmware, which takes out the development time. The chip is about half the cost of the component equivalent."

-by Margery Conner Teridian, www.teridian.com.

AND IF YOU AGREE TO INFINITE LIABILITY,

YOU GET A .00001% CHANCE OF DATING ME

PLUS A MINUTE TO PLAY

WITH AN UNIDENTIFIED

GIZMO.

#### **DILBERT By Scott Adams**

The self-calibrating 78M6618

power-measuring SOC has

an accuracy of greater than

±0.5% over a 2000-to-1

dynamic range.

OLYMPUS AND **CALIBRE SPEED** CLOSURE

In recent process generations, routers have used design-rule data from LEF (library-exchange-format) files to check routes on the fly in an attempt to produce DRC (design-rulechecking)-clean routes. Unfortunately, there are approximately 1500 rules, prescribing nearly 6000 operations, at the 45nm node, according to estimates from Mentor Graphics. Equally unfortunately, rules are emerging for which there are no provisions in LEF, so these rules are not available to the routing tools. The result is that routers are creating patterns that are not passing DRC-leading to iterations, frustrated rereading of the design rules, and manual routing of problem spots.

To address these issues, Mentor has introduced Calibre InRoute, an Olympus routing kernel that directly calls Calibre nmDRC, nmLVS (layout versus schematic), and DFM (design for manufacturing) to check its work. The mechanism is a dynamic API (applicationprogramming interface) that allows Olympus, when it has satisfied the rules in the LEF file, to pass parameters to the Calibre routines and invoke them. Calibre then works directly on the Olympus data set. The tool requires no wholesale importing or exporting of data through ASCII files.-by Ron Wilson Mentor Graphics, www. mentor.com.

### Remote manageability and security built in. The express lane is now open.

**Intelligence where you need it.** The Intel® Core™ processor with vPro™ technology lets you fast forward to the next generation of transaction devices with advanced management and protection capabilities. Get moving with the developer's playbook at **intel.com/embedded/intelligence**

### pulse

### Apple buys second chip company

pple recently acquired Intrinsity, a leader in low-power, static design, for a rumored total of \$121 million. Such an acquisition makes sense for the consumer-electronics leader because many in the industry suspect that Intrinsity is the CPU-core-technology provider for Apple's custom A4 microprocessor in the iPad. According to Linley Gwennap, founder and principal analyst of The Linley Group (www. linleygroup.com), Intrinsity engineers designed the company's Cortex-based Hummingbird processor under contract to Samsung (www.samsung. com), which manufactures the 1-GHz A4. "No one has announced a 1-GHz Cortex A8 CPU other than Samsung with the Hummingbird," he says.

lows Apple's 2008 purchase of PA Semi, a fabless chip designer that specialized in low-power PowerPC microprocessors, for \$278 million. Some people initially thought that Apple relied on the acquired PA Semi team to build the iPad's A4 processor. Gwennap notes, however, that the scenario is unlikely because a CPU usually takes three years to design, integrate, and validate. As such, he believes, PA Semi's technology has not been part of Apple long enough to be a design factor in the iPad, which Apple officially announced in January 2010, less than two years after it acquired PA Semi. Gwennap in a February blog post instead suggested the Hummingbird was behind the iPad's A4. Since then, several industry analysts have pointed to Intrinsity as the key to the A4.

Apple likely had future A4 design plans beyond the iPad in mind when making the purchase.

Still, Apple may have had its PA Semi acquisition in mind when purchasing Intrinsity. "Intrinsity's real expertise is more in the circuit design," says Gwennap. The company has spent years developing and patenting techniques to achieve high clock speeds at low power, whereas PA Semi's expertise is in more of the CPUarchitecture and -logic design. "[Apple] could use the Intrinsity circuit techniques to accelerate whatever CPU architecture the PA Semi guys have been working on," he says. "They could fit together pretty well."

Apple also likely had future A4 design plans beyond the iPad in mind when making the purchase. "It doesn't really make sense for Apple to invest this much money to develop CPUs for the iPad," Gwennap says. "The product sales are supposed to be in the millions this year, but they have a large and thriving iPhone business, so I would fully expect the A4 to be in the next-generation iPhone and potentially in the iPod touch, as well. When you put the three products-the iPad, iPhone, and iPod touchtogether, you're looking at a 50 million run rate. That's the kind of run rate that makes sense to design a custom processor for."-by Suzanne Deffree >Apple Computers Inc, www.apple.com.

The Intrinsity purchase fol- ke

### REDPINE, RENESAS TEAM ON EMBEDDED WI-FI

The notion of using Wi-Fi as a data-communications link in embedded systems has both appeal and complexity. Obviously, 802.11 is ubiquitous, mature, and well-understood, and inexpensive silicon abounds. Wi-Fi's developers, however, never intended it for mission-critical links. It is nondeterministic and not energy-efficient, and it requires trained operators to set up and maintain connections. It also requires certification from both the Federal Communications Commission (www.fcc.gov) and the Wi-Fi Alliance (www.wi-fi.org).

To address these issues, Redpine Signals has teamed with Renesas Electronics, combining Redpine's 802.11n module with your choice of several Super-H, RX, and R8C Renesas microcontrollers to offer plug-and-play embedded Wi-Fi. According to Venkat Mattela, chief executive officer of Redpine, the move to 802.11n resolves many of the issues with embedded Wi-Fi, and he believes that singlestream 11n is inherently robust and energy-efficient, significantly improving Wi-Fi's suitability for embedded use. "For embedded designers, the experience out of the box is vital," he says. "You can't assume the design will have a 2-GHz CPU or that your customer is willing to port a protocol stack to it. You can't assume a PC-knowledgeable person will be there to install the end system. Embedded Wi-Fi has to work with the designer's application, right out of the box." To this end, Redpine's SOC (system on chip)-the base of the module-includes a proprietary CPU core targeting lowpower execution of 802.11n protocol stacks. The baseband code, MAC (media-access control), TCP/IP (Transmission Control Protocol/Internet Protocol), and Wi-Fi Supplicant all reside on the SOC. The only required external software is a 2-kbyte driver on the external microcontroller. The module combines the SOC, power and RF components, and an antenna, so it is an out-of-the-box hardware/software package, carrying FCC and Wi-Fi certifications.

To minimize energy consumption, Redpine has both exploited the energy-conserving features of .11n and employed current thinking on low-power design. For example, the SOC uses the interval between packets to reduce the sample rate on the signal-chain ADC and uses the fact that the protocol stack runs locally on the chip to deduce opportunities to shut down blocks.

All this work gives the SOC a low energy profile. Redpine claims that the chip reaches 10  $\mu$ W in deep sleep and can remain operating at a supply of less than 3 mW. An active 115-kbps link, such as you would use to carry SPI (serial-peripheral-interface) traffic, requires less than 30 mW.

-by Ron Wilson

05.27.1(

Redpine Signals, www.redpinesignals.com. Renesas Electronics, www.renesas.com.

### 3-D system uses optical fiber to provide new options for photovoltaics

esearchers at the Georgia Institute of Technology have grown zinc-oxide nanostructures on optical fibers and coated them with dye-sensitized solar-cell materials to develop a new type of 3-D PV (photovoltaic) system. The approach could allow scientists to hide PV systems from view and locate them away from traditional locations, such as rooftops. "Using this technology, we can make photovoltaic generators that are foldable, concealed, and mobile," savs Zhong Lin Wang, a Regents professor at the Georgia Tech School of Materials Science and Engineering. "Optical fiber could conduct sunlight into a building's walls, where the nanostructures would convert it to electricity. This is truly a 3-D solar cell."

An article in Angewandte Chemie International details the researchers' findings (Reference 1), which DARPA (Defense Advanced Research Projects Agency, www.darpa. gov), the KAUST (King Abdullah University of Science & Technology Global Research Partnership (www.kaust.edu. sa/research/grc.html), and the National Science Foundation (www.nsf.gov) sponsored.

The researchers employed dye-sensitized solar cells, which use a photochemical system to generate electricity. They are inexpensive to manufacture, flexible, and mechanically robust, but their trade-off for lower cost is conversion efficiency lower than that of silicon-based cells. Using nanostructure arrays to increase the surface area available to convert light could help reduce the efficiency disadvantage, however, and give architects and designers new options for incorporating PV into buildings, vehicles, and even military equipment.

Fabrication of the new Georgia Tech PV system begins with the same type of optical fiber the telecom industry uses to transport data. First, the researchers remove the cladding layer. They then apply a conductive coating to the surface of the fiber before seeding the surface with zinc oxide. Next, they grow aligned zinc-oxide nanowires, much like the bristles of a bottle brush, around the fiber. They then coat the nanowires with the dye-sensitized materials that convert light to electricity.

Sunlight entering the optical fiber passes into the nanowires, where it interacts with the dye molecules to produce electrical current. A liquid electrolyte between the nanowires

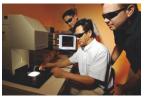

Researchers grow a brown, light-absorbing material for the solar generators on optical fiber (courtesy Gary Meek, Georgia Tech).

Researchers Benjamin Weintraub (left), Zhong Lin Wang (center), and Yaguang Wei (right) examine an image of their 3-D solar cell (courtesy Gary Meek, Georgia Tech).

collects the electrical charges. The result is a hybrid nanowire/ optical fiber system that can be as much as six times as efficient as planar zinc-oxide cells with the same surface area. "You have multiple light reflections within the fiber and multi-

ple reflections within the nanostructures," Wang says. "These interactions increase the likelihood that the light will interact with the dye molecules, and that [pro-Georgia Tech cess] increases the Regents professor Zhong Lin Wang efficiency." holds a prototype

Wang and his 3-E solar cell that team have reached could allow designan efficiency of ers to locate PV 3.3% and hope to systems away from reach 7 to 8% after rooftops (courtesy surface modification. Gary Meek, Georgia expect them to Tech). Although lower than

the efficiency of silicon solar cells, this efficiency would be useful for practical energy harvesting. If the researchers can achieve that goal, the potentially lower cost of their approach could make it attractive for many applications.

By providing a larger area for gathering light, the technique would maximize the amount of energy that strong sunlight produces and generate respectable power levels even in weak light. Using lenses to focus the incoming light could increase the amount of light entering the optical fiber, and the fiber-based solar cell has high saturation intensity. This new structure will offer architects and product designers an alternative PV format for incorporating into other applications. "We could eliminate the aesthetic issues of PV arrays on buildings," says Wang. "We

can also envision PV systems for providing energy to parked vehicles and for charging mobile military equipment where traditional arrays aren't practical."

Wang and his team have produced generators on optical fiber as long as 20 cm. "The longer the better because the longer the light can travel along the fiber, the more bounces

> it will make and the more it will be absorbed," says Wang. The researchers have been using traditional quartz optical fiber, but Wang would like to use less expensive polymer fiber to reduce the cost.

> Although the cells could find use in large PV systems, Wang doesn't soon replace sili-

con devices. He does, however, believe that they will broaden the potential applications for photovoltaic energy. "This [approach] is a different way to gather power from the sun," Wang says. "To meet our energy needs, we need all the approaches we can get."

-by Fran Granville Georgia Institute of Technology, www.gatech.edu.

#### REFERENCE

Weintraub, Benjamin, Yaguang Wei, and Zhong Lin Wang, PhD, Optical Fiber/Nanowire Hybrid Structures for Efficient Three-Dimensional Dye-Sensitized Solar Cells," Angewandte Chemie International, Volume 48, Issue 7, Oct 22, 2009, pg 8981, www3.interscience.wiley. com/journal/122659616/ abstract.

### VOICES The MathWorks' Silvina Grad-Freilich talks highperformance computing

The HPC [high-performance-computing] market will resume growth in the middle of this year, although change will be evolutionary, according to "IDC's Top 10 HPC Market Predictions for 2010," which the company presented earlier this year. To learn how HPC might affect the design community, *EDN* spoke with Silvina Grad-Freilich, parallel-computing marketing manager at The MathWorks.

#### What does The MathWorks offer that can help designers take advantage of HPC?

We have a set of tools called the Parallel Computing Toolbox, and these tools allow you to solve larger problems by using additional compute capacity. That additional compute capacity can be anything from the multiple cores in your desktop machine to clusters or grids. A second toolset is Matlab Distributed Computing Server, which allows users to scale the applications they develop to run on a cluster.

#### How can Matlab and Simulink users employ these tools?

Matlab users usually write their own code, but one of the premises is that they are domain experts more than programmers. One of the main reasons they came to Matlab is to basically have a development environment where they can rapidly develop a prototype. One of the things that these parallelcomputing tools allows them to do is stay in the same environment.

### What other support do you offer for parallel computing?

We have integrated other toolboxes with the Parallel Computing Toolbox. In the Statistics Toolbox and Optimization Toolbox, for example, there are already some functions we have parallelized. So if you write an application based on those functions, you don't need to change your application at all to be able to use all the cores in your machine or scale your application up to a cluster.

In addition to that feature, we provide APIs [application-programming interfaces] so that you as a Matlab user can also parallelize your own applications. For example, let's suppose that you have an application such as a parameter sweep or a Monte Carlo simulation that tests Matlab code over a set of parameters. In Matlab, that would be expressed by a for loop. To parallelize the application, you

just change the for loop to a parfor loop.

#### And what about Simulink?

Something very similar happens to Simulink. For example, the Simulink Design Optimization tool also works with the Parallel Computing Toolbox. With parallel computing integrated within Design Optimization, you can make use of the different cores in your machine or a cluster to run more simulations.

IDC predicts that x86 processors will dominate but GPUs (graphics-processing units) will gain traction. Does The MathWorks support GPUs?

Not yet, but we have a beta program running right now that started at the beginning of this year. Basically, we are inviting Matlab users to test our solution for GPUs. The program has been amazingly popular within our customer base.

Were there any surprising predictions raised in the

#### **IDC** presentation?

Not surprising, but interesting. One prediction is about how the challenge of highly parallel programming will increase, and we as programmers have seen all the time that programming a multicore machine is significantly harder than programming for a single-core machine, but what we are trying to do with our tools is to shield users from that complexity.

### What else did you take note of in the predictions?

One of the predictions A is that the HPC market will resume growth in mid-2010. That prediction is great to see. One thing we have said is that, during the recession and even now, our tools have been very successful. Even with all the changes in the economy and the recession and layoffs, people are looking for more and more ways to be more productive, and running our tools on highperformance computers is all about productivity.

-interview conducted and edited by Rick Nelson

### RAQ's

# Rarely Asked Questions

Strange stories from the call logs of Analog Devices

### Keeping Your A/D Converter Clocks Jitter Free

#### **Q**. How do I make improvements to my system clock or clock circuit so as to reduce jitter?

**A.** Jitter or noise on a clock signal can only corrupt an ADC's timing when present around the threshold region of the ADC's clock input. Increasing the slew rate of the clock signal decreases its transition time, thus reducing the amount of time that noise is present during the threshold period. This effectively reduces the amount of rms (root-mean-square) jitter introduced to the system. As an example, a 12-bit ADC requiring 100-fs minimum rms jitter for a 70-MHz analog input must have 1-V/ns slew rate.

So, minimizing jitter means improving the slew rate of the clock edge. One way to do this is to improve the clock source itself. A custom high-performance clock oscillator is typically used to characterize the baseline performance achieved by Analog Devices ADCs. Not all users of these high-speed converters can afford the cost or space required by a highperformance, oven-controlled, low-jitter oscillator, but available cost effective oscillators can achieve reasonable performance, even at high input frequencies. Care should be taken when selecting an "off-the-shelf" oscillator, though, as oscillator vendors do not always specify or measure jitter in the same way. A pragmatic way to determine which oscillator is best for the particular application is to collect a handful and test them in the system directly. By making this choice the only variable, performance can be predicted (assuming that the oscillator vendor maintains reasonable standards of quality control). Better yet is to contact the oscillator manufacturer to obtain

jitter- or phase noise data and get suggestions as to how to best terminate the device. Improper oscillator termination can seriously degrade the converter's spurious-free dynamic range (SFDR).

It is critical to understand the entire clock system in order to achieve the best possible performance from the converter. Decreasing the jitter of the system clock circuit can be achieved in many ways, including improving the clock source, as discussed, as well as filtering, frequency division, and proper choice of clock circuit hardware. Remember to pay attention to the slew rate of the clock, as this will determine the amount of noise that can corrupt the converter during the transition time. Minimizing this transition time can improve the converter's performance. Use only necessary circuitry to drive and distribute the clock because each component in the signal chain will increase the overall jitter. Finally, don't use "cheap" hardware; its performance is likely to be disappointing. One can't expect championship performance from a \$70,000 car outfitted with \$20 tires.

> To Learn More About Jitter Free Clocks

http://designnews.hotims.com/27744-101

**Contributing Writer Rob Reeder is a senior** converter applications engineer working in Analog Devices highspeed converter group in Greensboro, NC since 1998. Rob received his MSEE and BSEE from Northern Illinois University in DeKalb, IL in 1998 and 1996 respectively. In his spare time he enjoys mixing music, art, and playing basketball with his two boys.

For Analog Devices' Technical Support, Call 800-AnalogD

SPONSORED BY

#### BY BONNIE BAKER

### The best solution brings accuracy

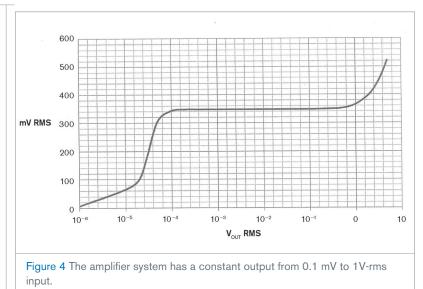

n my last article, I compared the throughput times of SAR (successive-approximation-register) and delta-sigma ADCs (**Reference 1**). I concluded that the throughput times—70k and 24k samples/sec—of PGA (programmable-gain-amplifier)-SAR systems and delta-sigma converters, respectively—are close. Which system is best? It looks like a draw with this evaluation, but what about accuracy?

Think of accuracy in terms of whether a system can produce the right output value. You can best describe the system accuracy with the dc specifications, such as offset, gain, and linearity. In this evaluation, use the appropriate system devices' minimum or maximum specification.

Once you refer the offset errors of each device to the input of each device, you can add them together. The equation for this calculation is available with the online version of this article at www.edn.com/100527bb. In a similar fashion, you can calculate a system's RTI (referred-to-input) gain error and linearity error.

Usually, you combine the uncorrelated dc errors, of gain, offset, and linearity, using an RSS (root-sumsquare) formula. The equation for this calculation is available with the online version of this article at www.edn. com/100527bb. Note that you should refer these errors to the system input.

In general, an SAR ADC's accuracy, or TUE (total unadjustable error), becomes worse with increased gain. This statement may not intuitively make sense, but remember that two factors are at work. First, increasing PGA gain decreases the system input's full-scale voltage range, and actual voltage LSB for 12-bit systems. Second, the absolute voltage errors from the op amp and ADC decrease. Unfortunately, the PGA offset voltage error remains constant.

Now consider a delta-sigma converter's TUE characteristics. Many readers of a previous column suggest that the delta-sigma units win out over PGA-SAR systems (Reference 2). As with any other ADC, deltasigma converters generate the offset, gain, and linearity dc errors. The key difference between applying a process gain with a delta-sigma converter and applying an analog gain with a PGA-SAR circuit is that the process gain does not multiply the offset error. On the other hand, the gain and linearity error is inversely proportional with increases in process gain. The end result is that the TUE decreases with increases in process gain. However, the TUE as a percentage of full-scale range remains constant.

For discussion purposes, Table 1 compares data from a PGA-SAR system and from a delta-sigma converter. The PGA-SAR system comprises the PGA116 PGA, the OPA350 operational amplifier, and the 12-bit ADS7886 ADC. The delta-sigma converter is the 24-bit ADS1258. In this evaluation, neither system performs to a 12-bit accuracy level, but the PGA-SAR combination is generally more accurate than the delta-sigma converter.

I challenge you to find two systems with comparable throughput rates in which the PGA-SAR system is generally less accurate than the delta-sigma converter over their entire gain ranges. Send your ideas to me at ti\_bonnie baker@list.ti.com.EDN

+ For the references cited in this column, go to www.edn.com/100527bb.

| TABLE 1 COMPARISON OF CONVERTER PERFORMANCE |                                     |                              |               |                                    |              |                                       |

|---------------------------------------------|-------------------------------------|------------------------------|---------------|------------------------------------|--------------|---------------------------------------|

| Baseline                                    |                                     |                              | PGA SAR       |                                    | Delta Sigma  |                                       |

| Analog or<br>process gain                   | System full-scale<br>range (V, RTI) | System LSB<br>size (µV, RTI) | TUE (µV, RTI) | TUE percentage of full-scale range | TUE (µV RTI) | TUE percentage<br>of full-scale range |

| One                                         | 5                                   | 1220.7                       | 8701          | 0.174                              | 25,000       | 0.5                                   |

| Two                                         | 2.5                                 | 610.35                       | 4368          | 0.175                              | 12,500       | 0.5                                   |

| Four                                        | 1.25                                | 305.18                       | 2203          | 0.176                              | 6250.01      | 0.5                                   |

| Eight                                       | 0.625                               | 152.59                       | 1121          | 0.179                              | 3125         | 0.5                                   |

| 16                                          | 0.3125                              | 76.29                        | 583           | 0.187                              | 1552,54      | 0.5                                   |

| 32                                          | 0.1563                              | 38.15                        | 319           | 0.204                              | 781.33       | 0.5                                   |

| 64                                          | 0.0781                              | 19.07                        | 194           | 0.248                              | 390.78       | 0.5                                   |

| 128                                         | 0.0391                              | 9.54                         | 138           | 195.63                             | 195.63       | 0.501                                 |

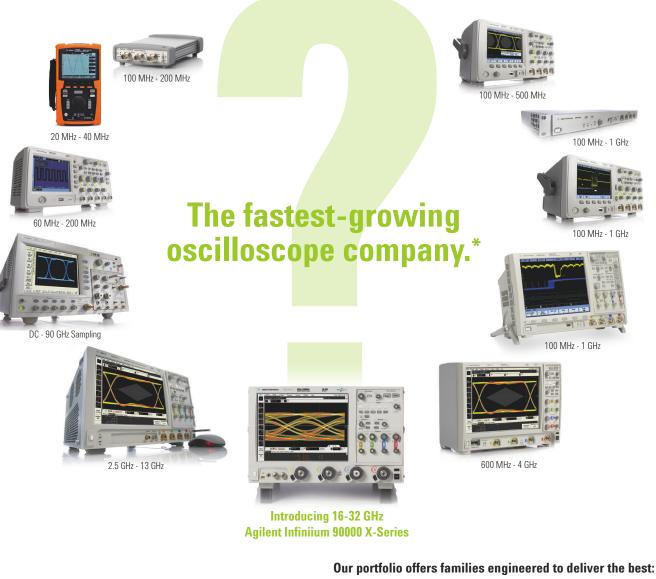

### Who makes the fastest real-time oscilloscopes?

- Best measurement accuracy

- · Broadest measurement capability

- Best signal visibility

- · More scope than you thought you could afford

Are you using the best scope? Take the 5-minute scope challenge and find out. www.agilent.com/find/scopecheck

u.s. 1-800-829-4444 canada 1-877-894-4414

INSIDE NANOTECHNOLOGY

### BY PALLAB CHATTERJEE, CONTRIBUTING TECHNICAL EDITOR

# Nanopatterning: getting the right objects small

he new materials and new phenomena that result from size are driving nanotechnology applications. One of the major challenges is creating these tiny objects in the shape and orientation to have control over these new characteristics. The leading methods of patterning at the nanoscale dimensions of 1 to 100 nm are lithography, nanoimprint-

ing, and self-assembly.

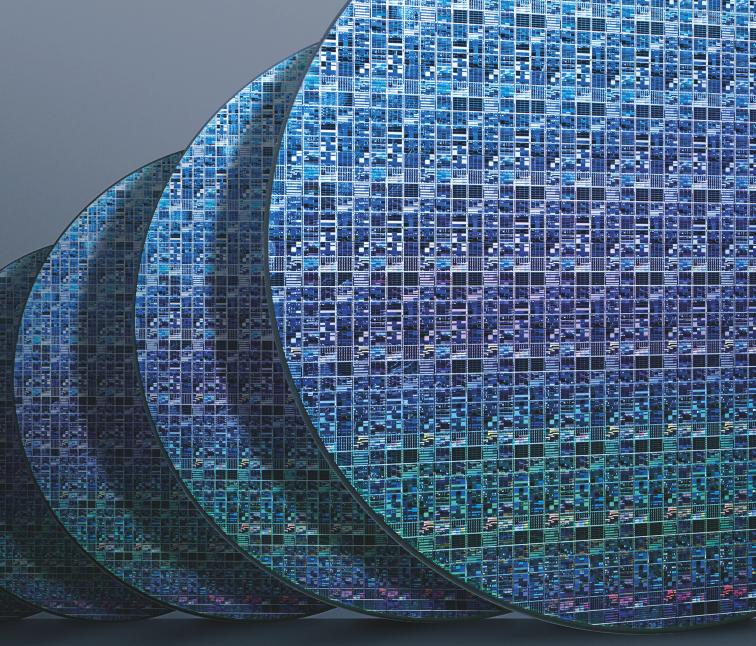

Designers have traditionally preferred lithography for IC and MEMS (microelectromechanical-system) design and creation. Optical lithography uses a series of lenses and a single light source to project a tiny image

of a scaled master image on a mask onto the substrate, which, in most cases, is a silicon wafer.

Discussions abound about when EUV (extreme-ultraviolet) lithography with a short-wavelength light source will replace optical lithography. Nevertheless, the use of double patterning, immersion lithography, and other multiple-imaging techniques is pushing 193-nm lithography to 32and 28-nm processes. Manufacturers such as Nikon have recently introduced lithographic equipment for the double-patterning applications. These techniques dominate the semiconductor arena due to their high throughput and systematic predictability of the output images.

Image patterning down to 25 nm is now possible at high throughput using nanoimprinting technology (**Figure** 1). These features can be complicated for both IC and hard-disk-drive applications. For production, manufacturers must print these features on both sides of the hard-drive platter. Nanoimprint technology provides a physical

Figure 1 Image patterning down to 25 nm is now possible at high throughput using nanoimprinting technology.

contact and may include J-FIL (jet-and flash-imprint-lithography) technology, which uses a UV-flash exposure with an intelligent, pattern-density-based resist-drop-pattern deposition system. The high throughput requires highquality master plates, with high accuracy and long manufacturing times using a Gaussian e-beam writer, and low-cost, high-resolution "working plates."

Manufacturers such as Molecular Imprints have recently introduced ma-

chines for the high-speed, low-cost creation of these working plates, extending the nanoimprint technology to traditional CMOS-silicon-wafer fabrication and to ultra-high-volume nanomedical applications. The working plates become the tools for the nanoimprinting machines that create patterns on the wafers.

The third leading method is blockcopolymer self-assembly, in which a machine simultaneously introduces multiple polymer chains of different materials to a surface. The polymers' interaction creates systematic, 3- to 50-nm patterns without any pattern postprocessing. The patterns are typically cylinders, circles, lines, or rings, depending on the density of materials. Researchers intend to use these patterns for electronics, in contacts and interconnect for the 16-nm and smaller nodes, as well as for solar and nanomolecular applications. The solar applications are seeking higherefficiency absorption patterns, which in turn will result in high-efficiency solar cells.

IC fabrication has been relying on lithographic processes since its inception in the early 1950s, and the technology is well-developed down through 45-nm geometries. Work is under way to push lithography from 45 to 16 nm. Nanoimprint technology has also been around for a while. It is in its third or fourth generation of equipment and materials and is starting to take prominence in the harddisk-drive markets as they approach terabit-per-square-inch densities. Current patterning is pushing this level with research to increase this figure to 10 Tbps/in.<sup>2</sup>. Self-assembly is still in the research stage and best suits systems using 16-nm and smaller lithographies, including the nanomedical market.EDN

Pallab Chatterjee is vice chairman of the IEEE San Francisco Bay Area Nanotechnology Council. You can reach him at pallabc@siliconmap.net.

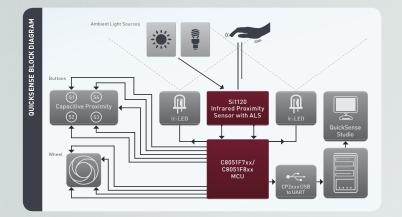

### TO TOUCH OR NOT TO TOUCH.

IT'S NOT A QUESTION, IT'S OUR SOLUTION.

Whether your application is gesture or touch-based, the QuickSense<sup>™</sup> portfolio of highly accurate and fastresponse touch, proximity and ambient light sense devices offers a more sensitive, better performing and lower power alternative to existing sensing solutions.

Silicon Labs makes it easy to program these sensing devices with the  $\mbox{QuickSense}$  Studio development software:

- Set up capacitive buttons, sliders and wheels using an intuitive software GUI that generates all the C code required for the selected functions

- Configure proximity and ambient light sensors through a comprehensive library of application programming interfaces (APIs)

- Thoroughly test and optimize user interfaces with real-time monitoring and adjustment tools

#### Si1120 AMBIENT LIGHT AND PROXIMITY SENSORS

- Up to 50 cm proximity range with a single pulse

Configurable ambient light and proximity

- measurement modes for range optimization

- High EMI immunity without shielded packaging

- Works in direct sunlight (100 klux)

- $\bullet$  Minimum reflectance sensitivity <1  $\mu W/cm^2$

- Operating temperature range: -40 to +85 °C

- Low power typical 10 µA current consumption

- Programmable 400/50 mA LED constant current driver output

#### C8051F7xx/8xx CAPACITIVE TOUCH SENSE MCUS

- Supports capacitive buttons, sliders, wheels and capacitive proximity sensing with 16 or 38 channels

- High-speed 25 MIPS CPU allows plenty of power for application code

- 10-bit, 500 ksps single-ended ADC

- Integrated temperature sensor

- Precision calibrated 24.5 MHz internal oscillator

#### TOUCH-LESS INTERFACE

- Enables users to interact with electronics with a simple gesture

- Enables entirely new form factors and usage models for common electronics

See how the QuickSense portfolio can help you spark fresh innovation in human interfaces. Download the white paper: "How to Design Capacitive Touch and Proximity Sense into Your Application." www.silabs.com/QuickSenseWP

# Apple's iPad: new computing form factor or passing fad?

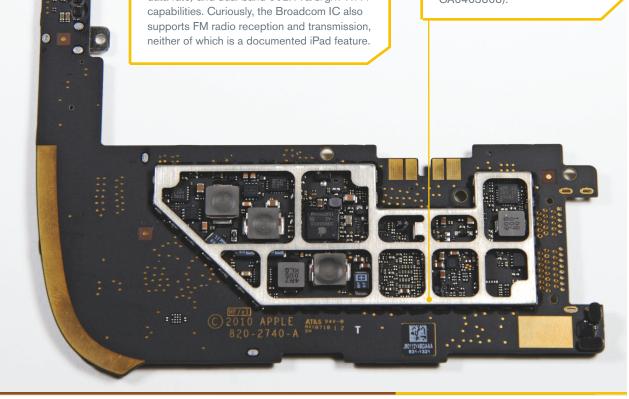

ablet-style computers running both Unix and Windows operating systems have for many years been an enduring presence on the tech landscape, primarily by virtue of the innumerable product failures. In early April, Apple began selling its first-generation OS X-based iPad. Is Apple's tablet destined for greater success than its predecessors, and what hardware building blocks compose it? My friends at iFixit (www.ifixit.com/Teardown/ iPad-Teardown/2183/1) helped me answer these questions.

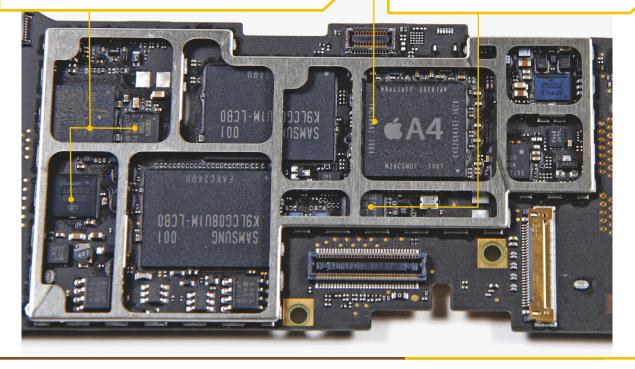

At approximately 4.5 in. wide, the iPad's primary PCB (printedcircuit board) is about the same size as that in an Apple handheld device, leaving plenty of room in the system cavity for the 25-Whr lithium-polymer battery. With the iPad, Apple also used many of the same chips it used in both the iPod touch and the iPhone, thereby giving a measure of validity to the oft-repeated observation that the iPad is little more than a big iPod touch.

The display interface employs Broadcom's BCM5973 microcontroller IC and BCM5974 capacitive-touchscreen-controller IC, plus Texas Instruments' CD3240A touchscreen-line-driver IC, rather than a more leading-edge approach with greater integration. This design choice likely reflects the fact that the iPad has a larger, higher-resolution screen than does either the iPhone or the iPod touch. It also has comparatively more PCB real estate.

### PRY FURTHER AT EDN.COM

Go to www.edn. com/pryingeyes for past Prying Eyes write-ups.

Die analysis and software profiling both suggest that the 1-GHz, ARM-based Apple A4 microprocessor combines a Cortex A8 single-core CPU and a PowerVR SGX 535 graphics processor. Although Apple more than two years ago bought PA Semiconductor-notably, the company's ARM-design expertise-persistent rumor suggests that Intrinsity, which Apple reportedly also acquired, spearheaded this project. The package also includes two 1-Gbit Samsung DRAM die, for 256 Mbytes of total system memory, the same amount as the latest-generation iPod touch.

> Other notable ICs include an NXT-developed DisplayPort and PCIe (Peripheral Component Interconnect Express) multiplexer/demultiplexer and an STMicroelectronics-supplied accelerometer. The identity and location of the silicon compass, an IC that made its debut in Apple's product line with the iPhone 3GS, are currently unknown. More generally, Apple's insistence on employing proprietary package markings complicates function and sourcing identification of many devices inside the iPad.

A CODEC CHIP THAT ACHIEVED 50% COMPRESSION IN DEVELOPMENT TIME.

THAT'S MODEL-BASED DESIGN.

To be first to market with a next-generation mixed-signal chip, the IC design team at Realtek used system models to continuously verify their design. The result: 50% less time to completion and a 50% market share. To learn more and to request the IBS study on Simulink ROI in Electronic Design, visit mathworks.com/mbd

©2010 The MathWorks, Inc.

This particular iPad is a Wi-Fi-only unit, lacking the 3G (third-generation) UMTS (Universal Mobile Telecommunications System) HSPA (high-speed-packet-access) cellular-data capabilities found in more expensive iPad versions. As such, you won't find relevant ICs, which mount on an add-in module in one corner of the unit. These ICs include Infineon's PMB 8878 X-Gold baseband chip and PMB 6952 dual-mode RF transceiver; Skyworks' Sky77340 poweramplifier module; Triquint's TQM616035A, TQM666032B, and TQM676031A power-amplifier/filter combinations; Numonyx's 36MY1EE NOR-flash memory containing additional system firmware; and Broadcom's BCM4750 implementing the A-GPS (assisted global-positioning-system) function that's also unique to the cellular-cognizant iPad.

The discrete wireless-communications module resides on the cable that interconnects the primary PCB and the bottom-edge dock connector. Broadcom's BCM4329 transceiver supports Bluetooth Version 2.1 EDR (enhanceddata-rate) and dual-band 802.11 a/b/g/n Wi-Fi capabilities. Curiously, the Broadcom IC also supports FM radio reception and transmission, neither of which is a documented iPad feature. Nonvolatile memory on the iPad comprises two 64-Gbit MLC (multilevel-cell) NAND-flash-memory ICs for 16 Gbytes of total resident storage on the primary PCB's front side; 32- and 64-Gbyte iPad variants are also available. An 8-Mbit SPI (serial-peripheral-interface) flash-memory IC, presumably containing system boot code, resides on the PCB's backside. This iPad employs Samsung-sourced NAND devices. whereas the FCC (Federal Communications Commission) characterized a unit that used Toshiba-fabricated silicon. The Atmel-stored system-firmware selection mimics Apple's choice on the second-generation iPod touch (see "Studying the secondgeneration Apple iPod touch," EDN, Sept 30, 2008, www.edn. com/article/CA6600223) and marks a departure from the Intel IC on the first-generation iPhone (see "Inside Apple's iPhone: more than just a dial tone," EDN, July 27, 2007, www.edn.com/article/ CA6463808).

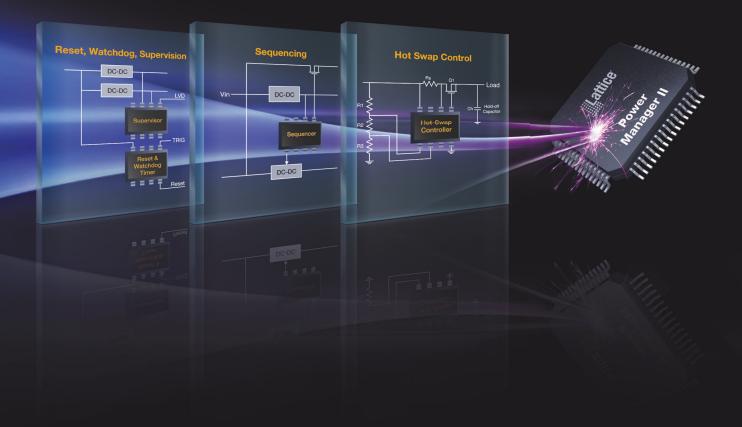

### Power Manager II. INTEGRATE POWER MANAGEMENT. LOWER COSTS.

Power Manager II features an innovative programmable core and precision analog sensors to reduce component count and increase reliability. Lattice programmability enables your power management design to meet changing requirements without major circuit redesign or a board re-spin.

Learn more about the cost-efficiencies of Power Manager solutions at: latticesemi.com/powermanager

#### Features

- Charge pumps for hot swap MOSFET control

- PLD for flexible supply sequencing and reset generation

- 0.2% error (typ.) programmable comparators for fault detection

- Differential sensing for centralized control

- 10-bit ADC with I<sup>2</sup>C interface for system monitoring

- High volume pricing starts at <\$1.00</li>

- And more ...

#### **Benefits**

- Integrate multiple functions to reduce BOM cost

- Increase fault coverage

- Reduce footprint

- Increase reliability

- Wide application coverage

- Reduce risks through programmability

- And more ...

latticesemi.com/powermanager

©2010 Lattice Semiconductor Corporation. All rights reserved. Lattice Semiconductor Corporation, L (& design), Lattice (& design) and specific product designations are either registered trademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries, in the United States and/or other countries. Other marks are used for identification purposes only, and may be trademarks of other parties

design

MATERIAI

FRESH IDEAS ON INTEGRATING MECHANICAL SYSTEMS, ELECTRONICS, CONTROL SYSTEMS, AND SOFTWARE IN DESIGN

### Handling the World Wide Web

HI)

Before the World Wide Web, engineers were handling webs at astonishing speeds.

he word "web" means different things to different people. To some, "web" conjures up images of Spider-Man, while most others may think of the ubiquitous World Wide Web. However, for many engineers, the word "web" brings to mind the pervasive and astonishing material web used in many processes that make the majority of the products we all use. Let's explore this overlooked material-handling application that is indispensable in so many diverse industries. And while we are doing that, let's ask the question, Why is there a gap and time lag between the latest technological advances in web handling and actual industrial practice, an observation not unique to this application?

VECHAT

#### Academic rigor and the best practices of industry need to be merged in an understandable, usable way for innovation to occur and result in tangible advances.

The economic advantage of manufacturing a material continuously instead of in batches is clear. The inputs and throughputs to continuous manufacturing processes are usually webs. A web is defined as a long, thin, flexible material with negligible bending stiffness about two of its three axes. Major classes of web materials include film, foil, food, paper, nonwovens, rubber, textiles, and composites of these. Materials range from centimeter-thick metals to micron-thick plastics; widths range from single, thin strands to more than 10m; and line speeds can reach more than 2,500m/min.

The goal of web handling is getting a web through a machine as fast as possible with minimum damage and waste, while preserving the web's properties. Web manufacturing forms the raw-material web (for example, paper making, film extrusion, textile spinning), while web converting (for example, coating, laminating, printing, sheeting) takes one or more web materials and permanently alters them in some fashion either by changing material properties or causing geometrical/physical changes. Web manufacturing and converting are often done by a combination of mostly art (trial and error) and a little bit of science, depending on the industry. However, all webs follow the same laws of physics—if we know the physics, we know the behavior. Web handling is an exact science with model-based design rules; all webs behave fundamentally the same way when pulled through a machine under tension. There even exists a wealth of literature and experts—D.H. Carlson, 3M Corp.; P.R. Pagilla, Oklahoma State University; and M.D. Weaver, Rockwell Automation—in this area. Monitoring and controlling web velocity and tension is a common web-handling challenge.

The use of a model-based design approach, rather than a trial-and-error design approach, is fundamental in modern mechatronic system design. Why is this approach not more widespread when applied to webs? There is a gap, and time lag, between the academic and research world and the world of industrial practice. More than 10 years ago, Dennis Bernstein wrote an article in the *IEEE Control Systems*

*Magazine* entitled "On Bridging the Theory/Practice Gap," in which he states that both sides contribute to the problem. The article was timely then and is even more so now.

So what needs to happen to bridge this gap? Academic rigor and industry best practices need to be merged in an understandable, usable way for innovation to occur and result in tangible advances. On the academic side, professors need to get out of their comfort zone and make each course, from freshman year through the graduate programs, an up-to-date fusing of academic rigor and best industrial practice with actual industry case studies as examples.

Too hard? Too challenging? This is what transformational engineering education is all about. On the industrial side, companies need to recognize that their competitive advantage comes from an inspired, educated workforce, and that should be their primary concern. Too often the training budget is the first to be cut, with the view that technological advances somehow arrive with the morning newspaper. Too harsh an assessment? I do not think so, and I do not believe the rest of the world thinks so either.EDN

Visit the Mechatronics Zone for the latest mechatronics news, trends, technologies, and applications: http://designnews.hotims.com/27744-542.

nechatronics

Kevin C Craig, PhD, is the Robert C Greenheck chair in engineering design and a professor of mechanical engineering, College of Engineering, Marquette University. For more mechatronic news, visit mechatronics zone.com.

## **Board Mounted Power**

Low cost

**High Reliability**

Short lead times

Industry standard footprints

### Industry standard DC/DC ranges

21201

B

### AC/DC low power board mounted ranges

ECL series

• 5 to 25 Watts Ultra compact size • Single outputs 3 - 48 VDC • Open-frame & encapsulated

2 to 40 Watts

- Wide 2:1 & 4:1 inputs

- Compact metal packages

#### Medical safety approvals

- 3 to 6 Watts

- Wide input range

- 3000 VAC reinforced insulation

- Low leakage current

#### ECP series

Download a FREE guide

to help select your DC/DC product at:

www.xppower.com/pdfs/DC-DC\_guide.pdf

- 20 Watts

- Low 0.73" profile

- Single and dual outputs

- No load output <0.3W</li>

Also available from www.newark.com

- LED drivers • 8 to 24 Watts

- Up to 1000 mA output Constant current output

- 95% efficiency

#### Surface mount power

- 1 & 2 Watts

- Regulated & unregulated versions

- ±10, 2:1 & 4:1 inputs

- Single & dual outputs

-.... -. 100-

Call or visit our website to request a copy of our latest Power Supply Guide and see our complete line of power products.

Newark

Toll free: 1-800-253-0490 Email: nasales@xppower.com

XP Power www.xppower.com

### "How can I tell if a power supply is reliable?"

### There's an indicator on the front.

It says "Agilent." With a typical MTBF of 40,000 hours, over half-acentury of experience, and with more than 250 models to choose from, Agilent's power supplies are the ones you can count on. In fact the array of our power supplies is so extensive, it wouldn't fit on this page. For clean, low-noise, programmable power to countless DUTs, there's an Agilent power supply with your name on it. Actually, it's our name on it, but you know what we mean.

> For free measurement tips and the Agilent Power Products brochure go to www.agilent.com/find/powertips

© 2010 Agilent Technologies, Inc.

### **Agilent Technologies**

**Agilent and our Distributor Network** *Right Instrument. Right Expertise. Delivered Right Now.*

866-436-0887 www.metrictest.com/agilent

### EXTREME INTEGRATION PACKS AN EXTENSIVE NUMBER OF COMMUNICATIONS FUNCTIONS INTO A HIGH-PERFORMANCE, LOW-AREA, LOW-POWER IC.

# RECONFIGURABLE SINGLE-CHIP RADIOS

#### BY JAN CRANINCKX AND PIET WAMBACQ • IMEC

n the future, mobile devices will have more and more access to all kinds of communications and multimedia services. They will have access not only to mobile-phone networks and the mobile Internet, but also to global-positioning systems, broadcasting services, WLAN (wireless-local-area-network) services, short-range connectivity, and many others. These future devices will also function in all kinds of situations—at home, in the office, during travel, and so on. ICs for these future mass-market wireless-communication consumer applications will be competitive only when they become small, energyefficient, and cost-effective.

#### **TERMINAL PERFORMANCE**

Ideally, a single mobile terminal should be able to accommodate all the communications functions a consumer would want. To ensure that such a terminal is low-cost, it is essential to minimize the area or form factor of the IC that implements the necessary communications functions within the terminal. The only way to achieve that goal is through extreme IC integration because IC integration can add features to a chip without increasing its area. Moreover, the IC should thus not just be a singlechip multistandard radio but instead a flexible radio chip. The RF part should integrate with the digital part of the radio in a single-chip SOC (system on chip). The flexible radio chip should be software-reconfigurable over a large range of communication standards, and it should be able to do the same job as several separate single-mode radios.

Due to its flexibility, a softwaredefined radio would also enable the new mobile terminals to choose the best standard for each situation. As a result, its flexibility will enhance the quality of the service and will enable the terminal to optimize its energy efficiency.

Integrating the RF part of the radio with the digital part onto a single IC is one of the main challenges. Engineers must perform this integration in a digital-scaled nanometer technology, in which it is essential to minimize the area of the RF part. People commonly assume that analog circuits do not scale with technology, which could endanger the cost advantage.

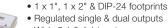

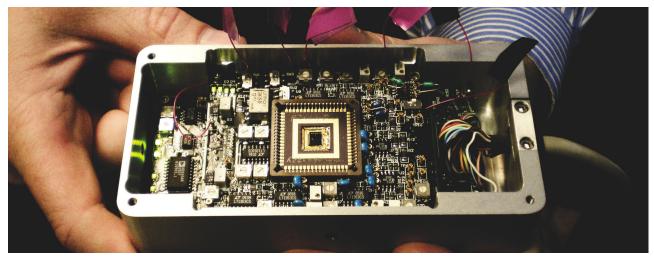

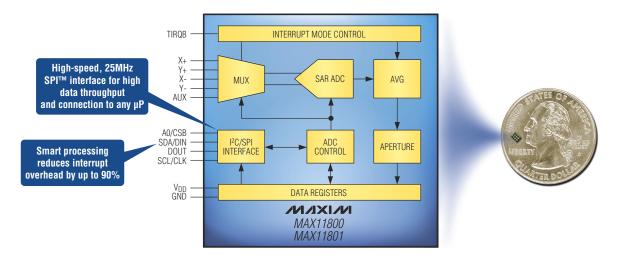

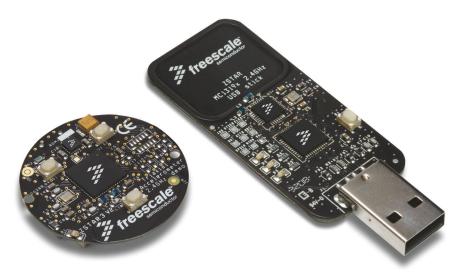

Researchers at IMEC (Interuniversity MicroElectronics Center), however, along with its partners, have succeeded in solving this challenge. The researchers have proved that the scaling of the analog part is possible and have demonstrated this ability by realizing a highperformance, low-area, reconfigurable single-chip radio. The new chip is a 5mm<sup>2</sup>, flexible RF transceiver in 40-nm, low-power digital-CMOS technology (**Figure 1**). The chip exhibits RF performance that is comparable with that of state-of-the-art multiple-chip radios (references 1 through 3). To achieve this size and high performance, the company used the benefits of aggressively scaled low-power CMOS technology, such as the high intrinsic speed of the nanoscale transistors and less variability between the transistors. Engineers combined the use of the technology with a fundamental rethinking of radio-circuit architectures and designs to ensure that the analog-unfriendly nature of nanoscale technology would not degrade performance.

#### **ANALOG CIRCUITS DO SCALE**

On-chip capacitors provide examples of analog's ability to scale down. Earlier generations of capacitors needed expensive technology options to create MIM (metal-insulator-metal) capacitors, but nanoscale CMOS technology and the progression in lithography techniques and metal stacks have resulted in MOM (metal-oxide-metal) capacitors. These capacitors enable a much higher capacitor density. MOM capacitors are purely digital, meaning that they are free, along with the normal digital processing. Hence, in new CMOS nodes, analog circuits do partially scale down in area.

Moreover, the technology's matching parameters improve along with the progression in the processing techniques. The better transistor matching per area is another argument that analog circuits do scale. Analog circuits profit from better process control, which results in smaller transistors that are now more identical to each other than were the transistors of 10 years ago. The result is a significant increase in the transistor density, minimizing the area and increasing the performance.

Analog's scaling benefits are limited, however. Therefore, most improvements in nanometer CMOS radio circuits must come from a fundamental rethinking of the front end's circuit and architectures. In this case, it is crucial to limit the large area penalty that is associated with the use of inductors for high-frequency operation. The best way to minimize the area would be to remove the inductors from the RF circuits. In some cases, you can now eliminate the use of inductors in the circuit design because the design uses 40-nm transistors. These nanoscale transistors have a much higher intrinsic speed than the transistors of larger nodes.

In other cases, you cannot eliminate the use of inductors because they are essential to maintaining the circuit's performance. In that case, you can minimize the area and maintain the circuit performance by designing circuit AT A GLANCE

A flexible, cost-effective radio chip will integrate RF and digital parts.

People often erroneously assumed that analog circuits do not scale.

LP (low-power) CMOS technology and a fundamental rethinking of radio-circuit architectures yielded a flexible single-chip device.

Purely digital MOM (metaloxide-metal) capacitors enable high capacitor density.

It is crucial to limit the area penalty associated with the use of inductors.

architectures using small inductors with a slightly lower quality. New low-noise amplifiers, for example, allow the use of low-Q inductors without degrading performance. Finally, in some cases, the use of inductors is unavoidable, as in, for example, VCOs (voltage-controlled oscillators). In this case, you can use circuit architectures that operate at higher frequency and that require smaller inductors and, hence, smaller area.

#### **DIGITAL CONTROL**

An equally important strategy for area limitation is the use of heavy digital control and digital compensation of the analog circuits. Whereas designers once used analog techniques to solve the variability in analog circuits, they can now use digital-control mechanisms. You use software to make the analog blocks digitally reconfigurable so that they can adapt themselves to the required performance and so that you can compensate for process variability.

You solve other analog imperfections that occur, such as mismatch and linearity errors, not by making the transistors larger but instead by using digital-signal processing—for example, by applying clever digital algorithms and calibration techniques. The transistors for this digital control are very small and thus involve practically no overhead cost with respect to area and power consumption.

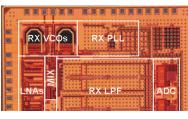

ADC=ANALOG-TO-DIGITAL CONVERTER LNA=LOW-NOISE AMPLIFIER LPF=LOWPASS FILTER MIX=MIXER PLL=PHASE-LOCKED LOOP PPA=PREPOWER AMPLIFIER RX=RECEIVER TX=TRANSMIT VCO=VOLTAGE-CONTROLLED OSCILLATOR

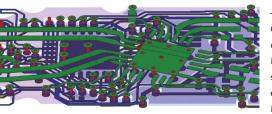

Figure 1 This prototype of a 5-mm<sup>2</sup> flexible RF transceiver in 40-nm, low-power digital-CMOS technology demonstrates that you can achieve state-of-the-art RF performance in low-power digital-CMOS technology.

The realization of a high-performance, low-area reconfigurable singlechip radio is essential for future mobile terminals in which low-cost, low-area, and energy-efficient approaches will be necessary in wireless-communication applications for the high-volume consumer market.EDN

#### REFERENCES